# HL1361CP00-Ln

## DFB Laser Diode Chip

#### **Sample Categories and Disclaimer**

**Functional sample** that has the suffix of "-F" or "-Fx" to the product number is a sample that is designed according to the customer's request. The purpose of this sample is to check and confirm the product feasibility. Thus the sample may be an R&D prototype or may be a modified current product. This sample may not be manufactured in qualified production lines nor using qualified parts. Basically Oclaro guarantees the requested performance of BOL (Beginning Of Life). Any qualification will not be applied.

#### **DESCRIPTION**

#### General

The HL1361CP00-Ln is an LR4 CWDM 1271/1291/1311/1331 nm Distributed Feed-Back (DFB) laser diode chip. Individual chip is designed for 10Gbit/s operation and for use in the dry N2 hermetic sealed package.

| PN*             | LR4 lane | Wavelength** (nm) | Notes               |

|-----------------|----------|-------------------|---------------------|

| HL1361CP00-L0   | 0        | 1271              | For MP use          |

| HL1361CP00-L1   | 1        | 1291              |                     |

| HL1361CP00-L2   | 2        | 1311              |                     |

| HL1361CP00-L3   | 3        | 1331              |                     |

| HL1361CP00-L0-F | 0        | 1271              | For initial samples |

| HL1361CP00-L1-F | 1        | 1291              |                     |

| HL1361CP00-L2-F | 2        | 1311              |                     |

| HL1361CP00-L3-F | 3        | 1331              |                     |

<sup>\*\*</sup> Actual wavelength range is specified separately.

#### **Pin Configurations**

Fig 1. Block Diagram (one LD chip)

Table 1. Pin Configurations

| Pin# | Description                 | Remarks |

|------|-----------------------------|---------|

| 1    | Laser anode (P electrode)   |         |

| 2    | Laser cathode (N electrode) |         |

### **MECHANICAL DIMENSIONS**

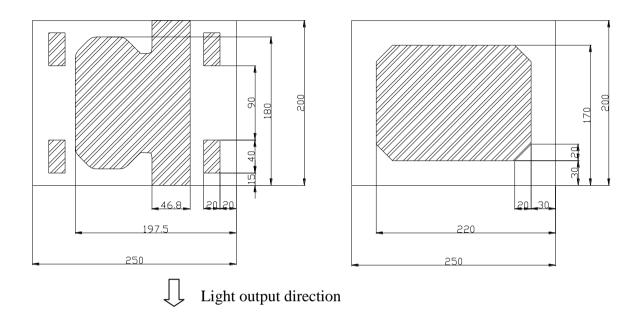

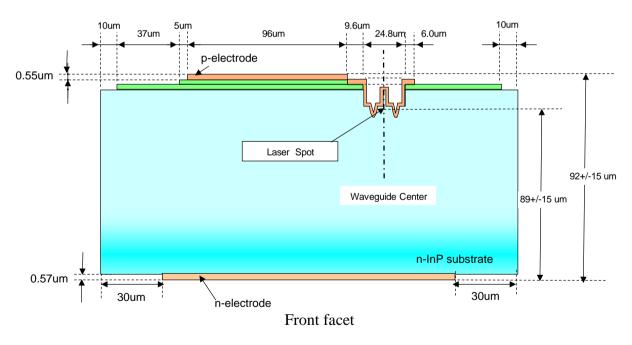

Individual chip size is 250  $\mu$ m x 200  $\mu$ m x 92  $\mu$ m. Fig. 4 shows a chip outline and metallization pattern. The Anode has typ. 0.55 $\mu$ m Au film and Cathode has typ. 0.57 $\mu$ m Au film respectively.

Fig.2 Top view (Anode)

Fig.3 Bottom view (Cathode)

(Outline: +/-20um)

Fig 4 Chip Outline and Dimensions

#### PERFORMANCE SPECIFICATIONS

#### **Absolute Maximum Ratings**

Since the HL1361CP00-Ln is a chip form, the performance will depend on not only chip performance but also its assembling process. If the chip is assembled in a proper way, the performance described in Table 2 can be expected but these are not guaranteed values. Oclaro assumes no responsibility for those reliability when they are assembled and/or tested in customer Tc means submount temperature when the chip mounted on Oclaro standard sub-mount soldered on heat sink.

Table 2. Absolute Maximum Ratings (Tc=25°C, unless otherwise specified)

|   | Absolute Maximum Rating      | Min | Max | Unit |              |

|---|------------------------------|-----|-----|------|--------------|

| 1 | Storage temperature          | -40 | 85  | C    |              |

| 2 | 2 Operating temperature      |     | 95  | C    |              |

| 3 | 3 Laser forward bias current |     | 150 | mA   |              |

| 4 | 4 Laser reverse bias voltage |     | 2   | V    |              |

| 5 | Die binding temperature      | -   | 350 | C    | (< 4 s) Note |

Note: Recommended condition: 320 C max and 4 s max.

### **Optical and Electrical Characteristics**

Since the HL1361CP00-Ln is a chip form, the performance will depend on not only chip performance but also its assembling process. If the chip is assembled in a proper way, the performance described in Table 3 can be expected but these are not guaranteed values.

Table 3. Expected Optical and Electrical Characteristics (Tc= -5C to 85C, unless otherwise specified, Condition at CoC (Chip on testing carrier))

| No       | Optical and Electrical<br>Characteristics | Min                                                                      | Тур | Max                                | Units        | Notes                                                                   |  |

|----------|-------------------------------------------|--------------------------------------------------------------------------|-----|------------------------------------|--------------|-------------------------------------------------------------------------|--|

| 1        | Lane wavelength range                     | 1264.5 - 1277.5<br>1284.5 - 1297.5<br>1304.5 - 1317.5<br>1324.5 - 1337.5 |     | 1284.5 - 1297.5<br>1304.5 - 1317.5 |              | nm                                                                      |  |

| 2        | Lane wavelength range at 25 C             | 1269±1.5<br>1289±1.5<br>1309±1.5<br>1329±1.5                             |     | nm                                 | @ 25C I=33mA |                                                                         |  |

| 3        | Wavelength temperature coefficient        |                                                                          | 0.1 | 0.11                               | nm/degC      |                                                                         |  |

| 4        | Side-mode suppression ratio (SMSR),       | 35                                                                       | -   | -                                  | dB           | @1 C I=33mA<br>@85 C I=70mA                                             |  |

| 5        | Threshold current                         | -                                                                        | 8   | 15                                 | mA           | @ 25C                                                                   |  |

| <i>J</i> | Threshold current                         | -                                                                        | 20  | 28                                 | mA           | @ 95C                                                                   |  |

|          | CI CC' :                                  | -                                                                        | 0.3 | -                                  | W/A          | @ 25C<br>I=Ith+5mA to Ith+50mA                                          |  |

| 6        | Slope efficiency,                         | 0.11                                                                     | -   | -                                  | W/A          | @ 95C<br>I=Ith to 70mA                                                  |  |

| 7        | Mask Margin<br>(IEEE 10.3Gb/s)            | 20                                                                       | -   | -                                  | %            | @25C I=Ith+25mA<br>PRBS=2 <sup>31</sup> -1,<br>1k waveforms<br>ER=4.5dB |  |

| 8        | Effective serial resistance               | -                                                                        | 7   | -                                  | Ohms         | @ 95C I=50mA                                                            |  |

| 9        | Laser forward voltage                     | -                                                                        | 1.5 | 2.0                                | V            | @ 95C I=70mA                                                            |  |

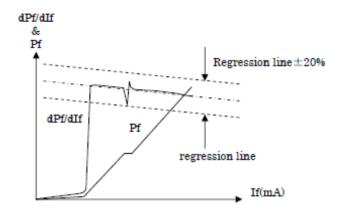

| 10       | Kink deviation                            | -                                                                        | -   | 20                                 | %            | I=Ith+5 to 100mA<br>See figure 5                                        |  |

| 11       | Far field divergence, Vertical,           | -                                                                        | 35  | 45                                 | degrees      | @ 95C I=70mA                                                            |  |

| 12       | Far field divergence, Horizontal,         | -                                                                        | 32  | 40                                 | degrees      | @ 95C I=70mA                                                            |  |

Note: Tc means sub-mount temperature when the chip mounted on Oclaro standard sub-mount soldered on a heat sink.

Fig 5 Kink definition

#### **Chip Test Specification**

Oclaro (supplier) will perform 100% probe testing on the chips described in Table 4 below. Only chips that pass the criteria in Table 4 will be shipped. The test will be done in bar or chip form using pulsed driving current.

Although chips pass the criteria described in Table 4, Oclaro assumes no responsibility for those performance, yield and reliability when they are assembled and/or tested in customer (buyer). Ts means stage temperature in pulse chip test.

Parameter Remark No. Symbol Condition Min Unit Max Threshold current  $I_{th}$  $T_s=85^{\circ}C$ 21.5 Note1 mA 2 Slope efficiency  $T_s=85^{\circ}C$ , 0.087 W/A Note2 Eta  $I_F=67.5mA$ 3  $T_s=25^{\circ}C$ 1268.7 1271.7 Peak wavelength  $\lambda_{p}$ nm  $I_F=67.5mA$ (L0)  $T_s=25^{\circ}C$ Peak wavelength 1288.8 1291.8 nm (L1) $I_F=67.5mA$  $T_s=25^{\circ}C$ Peak wavelength 1309.0 1312.0 nm (L2) $I_F=67.5\text{mA}$ Peak wavelength  $T_s=25^{\circ}C$ 1329.3 1332.3 nm  $I_F=67.5mA$ (L3)dB 4 Side mode **SMSR**  $T_s=25$ °C 35 suppression ratio  $I_F=67.5mA$  $T_s=85^{\circ}C$ 35 dB  $I_F=67.5mA$

Table 4 Chip test criteria

Note 1 21.5 mA=28 mA x A, A= Temperature correlated factor 0.782 Note 2 0.087 W/A=0.11W/A x B, B= Tester correlated factor 0.792

### **Wafer Verification Test**

Oclaro will perform hard screening (Burn-In), DC measurement and AC measurement using chips mounted on Oclaro standard submount soldered on heat sink. Only the chips that passed the criteria described in this "Wafer Verification Test" section will be used. Only the chips from wafers meeting the minimum yield described in Table 5 will be shipped.

Table 5 Criteria in wafer verification test

| Parameter                          | Condition                                                                               | Pass Criterion                                                                                          | Minimum<br>Number or<br>Yield |

|------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------|

| LD chip mount                      | -                                                                                       | -                                                                                                       | 20pcs                         |

| Start Burn-In test                 |                                                                                         |                                                                                                         |                               |

| Optical Purge test                 | 25°C, 120mA, ACC 3min.                                                                  | $\begin{split} & \Delta I_{th} \leq +5\%, \Delta Po \\ &\leq +10\%, \Delta Eta \leq +10\%. \end{split}$ |                               |

| Electrical Purge test              | 100°C, 150mA, ACC 20h                                                                   | -                                                                                                       |                               |

| APC Test                           | 95°C, 70mA, APC 100h,<br>(I <sub>op</sub> @100h-I <sub>op</sub> @0h/I <sub>op</sub> @0h | $-2\% \leq \Delta I_{op} \leq +0.5\%$                                                                   |                               |

| Pass Burn-In test                  |                                                                                         |                                                                                                         |                               |

| Start DC test                      |                                                                                         |                                                                                                         |                               |

| Threshold current                  | T <sub>c</sub> =95°C                                                                    | I <sub>th</sub> ≤28mA                                                                                   |                               |

| Slope efficiency                   | $T_c=95$ °C,<br>Eta=Po(70mA)/(70mA- $I_{th}$ )                                          | Eta≥0.11W/A                                                                                             |                               |

| Forward voltage                    | T <sub>c</sub> =1°C, I <sub>o</sub> =33mA<br>T <sub>c</sub> =95°C, I <sub>o</sub> =70mA | V <sub>op</sub> ≤1.8V                                                                                   |                               |

| Kink deviation,                    | T <sub>c</sub> =1°C and 95°C, Ith+5 to 100mA                                            | kink free                                                                                               |                               |

| Peak wavelength                    | $T_c=1$ °C, $I_o=33$ mA                                                                 | 1265.2nm≤λp≤1277.5nm                                                                                    |                               |

| L0                                 | T <sub>c</sub> =95°C, I <sub>o</sub> =70mA                                              | 1265.2nm≤λp≤1277.5nm                                                                                    |                               |

| L1                                 | $T_c=1$ °C, $I_o=33$ mA                                                                 | 1285.2nm≤λp≤1297.5nm                                                                                    |                               |

|                                    | T <sub>c</sub> =95°C, I <sub>o</sub> =70mA                                              | 1285.2nm≤λp≤1297.5nm                                                                                    |                               |

| L2                                 | $T_c=1$ °C, $I_o=33$ mA                                                                 | 1305.2nm≤λp≤1317.5nm                                                                                    |                               |

|                                    | $T_c=95$ °C, $I_o=70$ mA                                                                | 1305.2nm≤λp≤1317.5nm                                                                                    |                               |

| L3                                 | $T_c=1$ °C, $I_o=33$ mA                                                                 | 1325.2nm≤λp≤1337.5nm                                                                                    |                               |

|                                    | $T_c=95^{\circ}C, I_o=70\text{mA}$                                                      | 1325.2nm≤λp≤1337.5nm                                                                                    |                               |

| Side mode suppression ratio        | T <sub>c</sub> =1°C, Io=33mA<br>T <sub>c</sub> =95°C, I <sub>o</sub> =70mA              | SMSR≥35dB                                                                                               |                               |

| Beam divergence angle (Horizontal) | T <sub>c</sub> =95°C, I <sub>o</sub> =70mA                                              | FWHM_H≤36deg                                                                                            |                               |

| Beam divergence angle (Vertical)   | T <sub>c</sub> =95°C, I <sub>o</sub> =70mA                                              | FWHM_V≤40deg                                                                                            |                               |

| Pass DC test                       |                                                                                         |                                                                                                         | 10 of 20pcs (50%)             |

### **OTHER SPECIFICATIONS**

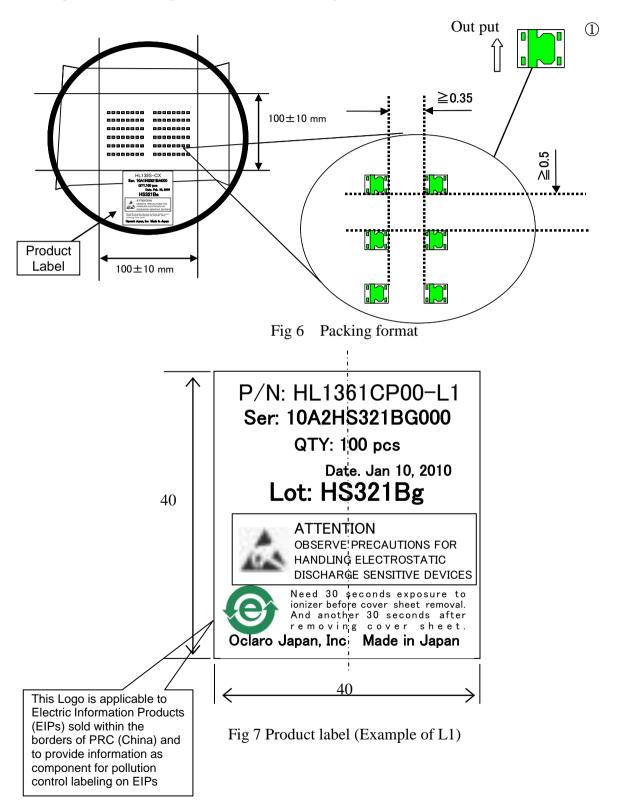

#### Packing and label

The products will be packed as described in Fig. 6 below.

]

The plastic bag is vacuum-packed.

Fig 8 Packing bag (Example)

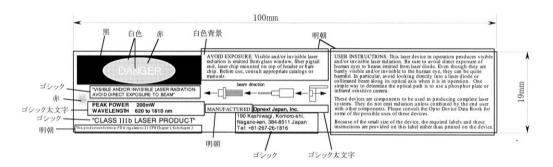

Fig 9 Danger Label (Example)

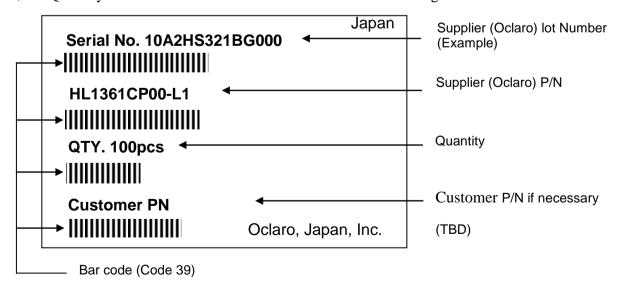

Bar code label is on plastic bag for each shipment form. Supplier Product Name, Supplier lot number, the Quantity and Customer Part Number are on it. Please see Fig. 8. 40x 80 mm

Fig. 10 Bar code label on outer plastic bag (Example of HL1361CP00-L1)

### **Revision History**

| Rev | Date            | Page/Line/Fig/Table | Modification | Note |

|-----|-----------------|---------------------|--------------|------|

|     |                 |                     |              |      |

| 0.0 | Nov. 20th, 2014 |                     |              |      |

|     |                 |                     |              |      |